## INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

### Design and Implementation of 1-bit Pipeline ADC in 0.18um CMOS Technology Bharti D.Chaudhari<sup>\*1</sup>, Priyesh P.Gandh<sup>i2</sup>

<sup>\*1</sup> PG Student, <sup>2</sup>Assistant Professor, L.C.institute of Technology, Bhandu, India

Chaudhari.bharti18@gmail.com

#### Abstract

This paper present the design of a single bit Pipeline Analog-to-Digital Converter (ADC) which is realize using CMOS technology. In this paper, a 1-bit Pipeline ADC is implemented in a standard TSMC 0.18um CMOS technology using Mentor Graphics Tool. 1-bit Pipeline ADC is design using  $\pm 1.8V$  power supply and simulation result is plotted using Mentor Graphics Tool.

This paper firstly elaborate about basic introduction of ADC and different ADC architecture and its application. Further Design of 1-bit Pipeline ADC is to be proposed which consist of sample and hold, DAC, Op-amp and Comparator as a key component in Pipeline ADC.

Keywords: CMOS technology, Comparator, Op-amp, Mentor Graphics Tool.

#### Introduction

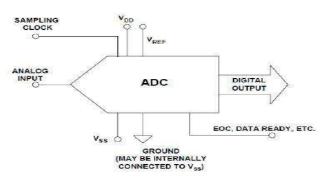

Analog-to-digital converters (ADCs) are very important building blocks in modem signal processing and communication systems. For signal processing, digital domain is preferred over analog domain because of its advantages such as noise immunity, storage capability, security etc. For long distance, digital communication is more reliable due to regenerative repeater. Due to these, today nearly all modern electronics are primarily digitally operated, allowing for advanced digital signal processing (DSP). But the real world signals such as signals coming from various transducers are analog in nature. This analog signal must be converted into digital to allow digital signal processing. This is done by Analog to Digital Converter (ADC) as shown in Figure 1. Similarly after signal processing in digital domain, the signal is converted back into analog. This is required for the transducer such as speaker. It is done by Digital to Analog converter (DAC). The applications of ADC include DC instruments, process control, thermocouple sensors, modems, digital radio, video signal acquisition etc. The ADC should be featured with low power and higher speed due to many reasons. First the rapid advent of battery operated portable system requires low power dissipation in order to prolong battery life, and a minimum number of battery cells to reduce the volume and weight of the system. Another reason is the smaller feature sizes offered by today's VLSI technology.

#### Fig.1 Ideal Block Diagram of Digital to Analog Converter <sup>[3]</sup>.

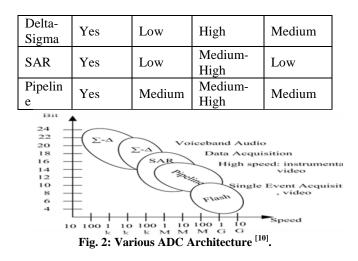

Different ADC architecture and its application are summarization in table 1. Among various ADC architectures, the pipelined ADC has the attractive feature of maintaining high accuracy at high conversion rate with low complexity and power consumption. Therefore it is used extensively in high-quality video systems, high speed data acquisition systems and high performance digital communication systems where both precision and speed are critical.

| Table 1: Com | parison of AD | C Architectures |

|--------------|---------------|-----------------|

|--------------|---------------|-----------------|

| Archit<br>ecture                  | Latenc<br>y | Speed           | Accuracy       | Area            |

|-----------------------------------|-------------|-----------------|----------------|-----------------|

| Flash                             | No          | High            | Low            | High            |

| Foldin<br>g/inter<br>polatin<br>g | No          | Medium<br>-High | Low-<br>Medium | Medium-<br>High |

http://www.ijesrt.com(C)International Journal of Engineering Sciences & Research Technology [1367-1371]

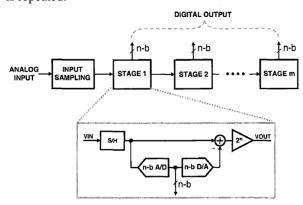

#### **Architecture of Pieline ADC**

Typical pipeline architecture is illustrated in Figure 3. Each stage has the four elements of a SHA, a sub-ADC, a sub-DAC and an inter-stage gain amplifier. The operation of a single stage consists of four steps. First, the input signal is captured by the sample and hold amplifier. Second, this signal is quantized by the sub-ADC, which produces a digital output. Third, this digital signal goes to the sub-DAC which converts it to an analog signal. This analog signal is subtracted from the original sampled signal thereby, leaving a residual signal. Fourth, this residual signal is increased to the full scale through the inter-stage amplifier. The residual signal is passed to the next stage and the procedure mentioned above is repeated.

Fig. 3: Generalized Pipeline ADC Architecture <sup>[3]</sup>.

# VLSI Implementation Of The 1-Bit Pipeline ADC

#### A. 1- Bit Single Stage of Pipelined architecture

This stage is consist of sample and hold circuit followed by 1-bit ADC, 1-bit DAC, subtracted and multiplier. The analog signal will be sampled and fed to the comparator acts as the 1-bit ADC that would give the 1-bit digital output. Before giving to the comparator the sample signal should lift to the .9V of the DC voltage so that the comparator can compare the value to the threshold voltage and give the output. The digital output again converted to the analog value through the 1-bit DAC Uses two reference voltage levels. This converted value will be subtracted from actual sampled signal to produce an error signal using a difference circuit. This signal often called as residue signal. This residue signal again multiplied by two with an open loop amplifier. The sub tractor and the multiplier are working at 100 MS/s.

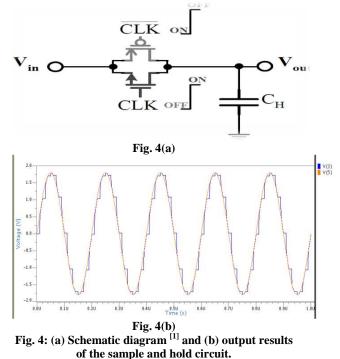

#### Sample and Hold Circuit

SH circuit can be realized using only a transmission gate and a capacitor. The operation of this circuit is very straightforward. Whenever CLK is high, the TG is ON, which in turn allows  $V_{OUT}$  to track  $V_{IN}$ . When CLK is low, the TG is OFF. During this time,  $C_H$  will keep  $V_{OUT}$  equal to the value of  $V_{IN}$  at the instance when CLK goes low. Implemented sample and hold is depicted in Figure 4(a).

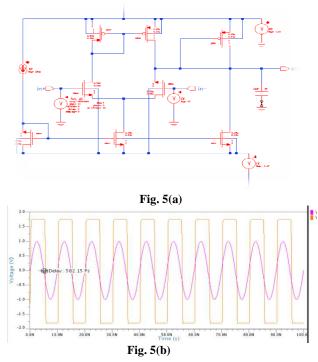

#### Design of CMOS Comparator

The Pipelined ADC consists of a 1-bit ADC which is composed of a comparator and a D-flip-flop. The design of comparator is similar enough to that of an Op-amp .The only difference is the use of the compensation network consists of resistor and capacitor and extra multipliers on a biasing NMOS device. The comparator does not need the compensation network because its only function is to switch from rail to rail. Stability is not needed as it

http://www.ijesrt.com(C)International Journal of Engineering Sciences & Research Technology [1367-1371] will only slow down the switching speed. When a sine wave is input to the circuit, the comparator switches from positive rail to negative rail.

Fig. 5: (a) Schematic diagram and (b) output results of the comparator circuit

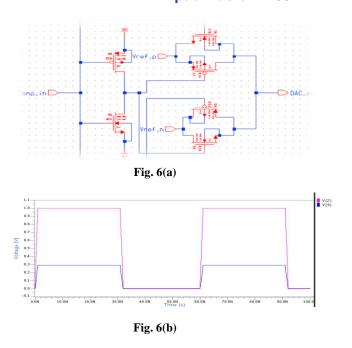

#### 1-Bit Digital-to-Analog Converter

Basically the 1-bit DAC can be implemented using simple 2X1 analog multiplexer. Here the multiplexer has to select  $\frac{\text{Vref}}{2}$  Volt or 0 Volt depending on the output of the comparator which acts as a selection line.

Here in implementation of 1-bit DAC, two TGs are used as shown in Figure 6(a). Inputs to these TGs are  $\frac{Vref}{2}$  and ground, while the outputs are connected together. Based on the comparator output  $\frac{Vref}{2}$  or zero voltage is available at the output of DAC. The control signals for TGs are comparator output and its inverted output obtained by an inverter. In this design analog input to the DAC are 1V and 0V. Based on comparator output (+1.8V or -1.8V) one of the analog inputs will be available at the output. This is clearly observed in Figure 6(a).

Fig. 6: (a) Schematic Diagram and (b) output waveform of 1-Bit DAC

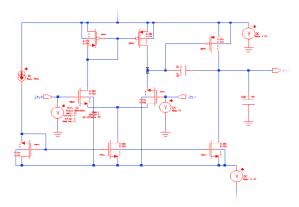

#### Two stage Operational Amplifier

The operational amplifier that the integrator uses must have the high gain to effectively carry out a smooth integration as well as a large enough bandwidth to support the high frequency sine waves it will be integrating. The OpAmp operates at the clock frequency, since the differences are being integrated over the region of time. Therefore, the gain bandwidth product of the OpAmp must be greater than one at the clock frequency to effectively pass the signal. The amplifier used is shown in figure. The key thing to note to about the amplifier is the frequency compensation network which is used to push the high frequency zero out of the pass band of the Opamp.

In amplifier, using proper capacitance and applying negative feedback, gain is adjusted to 2. This is because each stage is of 1-bit. If the stage is of n-bit then gain will be

2n.

Fig.7: Design of Two Stage Operational Amplifier.

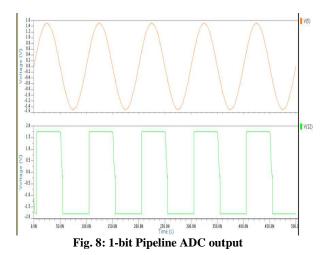

#### **Result Analysis**

The circuit design of sample and hold, Comparator and DAC Op- amp, for 1-bit Pipeline ADC have been developed and implemented by using 0.18um CMOS Technology.

The whole 1-bit Pipeline ADC subsystem works very well under the following conditions.

Table 2.Different measured parameter in 180nm

| PARAMETER                | VALUE |

|--------------------------|-------|

| POWER SUPPLY(V)          | 1.8v  |

| INPUT<br>FREQUENCY(MHZ)  | 10    |

| OPAMP GAIN(DB)           | 60    |

| POWER<br>DISSIPATION(mW) | 2.806 |

#### Conclusions

In present work, An 1-bit Pipeline analog-to digital converter system has been designed and simulated in standard TSMC 1.8um CMOS Technology. The circuits are simulated in SPICE with MOSIS Level-53 MOS model parameters. For simulation I used Power supply voltage is VDD=1.8v and sampling rate is 100Ms/S and after simulation Gain of Op-Amp is 60dB and Power dissipation s 2.706mW.

#### **References**

- [1] Christian Jesus B.FAYOMI, Gordon W.ROBERTS, "Design and Characterization of Low Power Analog Switch without the Need for Clock Boosting," IEEE Circuits and Systems, Vol.3, 25-28 July 2004.

- [2] Jian-feng Wang1, Ji-hai Duan2, "Design of An Ultra High-Speed Voltage Comparator,"IEEE Circuits, Communications and System (PACCS), Vol.2, 1-2 Aug. 2010.

- [3] Jaydip.H.Chaudhari , Gireeja D.Amin ," Design and Simulation of 1-bit Sigma Delta ADC in 0.18um CMOS Technology, "International Journal of Computer Applications & Information Technology Vol. II, Issue I, January 2013.

- [4] Thomas Liechti, Armin Tajalli, Omer Can Akgun, Zeynep Toprak, and Yusuf Leblebici, "A 1.8V 12-bit 230-MS/s Pipeline ADC in 0.18µm CMOS Technology," IEEE Circuits and Systems, Nov. 30 2008-Dec. 3 2008.

- [5] D. Meganathan, Axel Jantsch, "A Low-Power, Medium-Resolution, High-Speed CMOS Pipelined ADC,"IEEE NORCHIP, 15-16 Nov. 2010.

- [6] D. Meganathan, AmrithSukumaran, M.M.DineshBabu, S.Moorthi, and R.Deepalakshmi "A systematic design approach for low-power 10-bit 100 MS/s pipelined ADC" Microelectronics Journal, 2009.

- [7] Junhua Shen and Peter R. Kinget, Senior Member, "A 0.5-V 8-bit 10-Ms/s Pipelined ADC in 90-nm CMOS,"Solid-State Circuits, IEEE Journal of Vol.43, Issue: 4,April 2008.

- [8] Ali Mesgarani, Ahmet Tekin, Suat U. Ayl, "A High-Speed and Low-Power Pipelined Binary Search Analog to Digital Converter," IEEE Circuits and Systems (MWSCAS), 7-10 Aug. 2011. Poonam,

http://www.ijesrt.com(C)International Journal of Engineering Sciences & Research Technology [1367-1371] Manoj Duhan, Himanshi Saini "Study and Analysis of Low Voltage Low Power Pipelined ADC" International Journal of Advanced Trends in Computer Science and Engineering, 2012.

[9] Appa Rao M., Dr. Ramana Reddy P., Cyril Prassna raj P. "Design and implementation of Low power 12-bit 100MS/s pipelined ADC Using open loop Residue Amplifier," Global Journal of Researches in Engineering (F) Vol.XII, issue XI,2012.